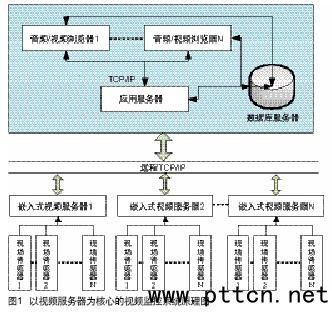

主页(http://www.pttcn.net):视频服务器通用结构及其智能化设计设想 本文针对视频服务器的通用结构做了详细地探讨,并对该产品未来的智能化设计提出了一些设想,希望能为广大读者提供参考。 音视频压缩技术是视频服务器和智能视频监控系统中的关键技术。在数字多媒体压缩(特别是视频压缩)领域内有很多国际标准(如ISO/ITU-T技术委员会的JPEG标准、CCITT制定的H.26X标准以及著名的MPEG标准等)。其中,MPEG-4标准的主要特点是可对图像中的内容进行编码,其核心是基于内容尺度可变性(Content-based scalability)即可以给图像中的各个对象分配优先级。其中,比较重要的对象用较高的空间和(或)时间分辨率表示;对于比较低的比特率应用系统来说,尺度可变性是一个关键的因素,因为它提供了自适应可用资源的能力。例如,该特性允许对具有较高优先级的对象用可接受的质量进行显示,次优先级的对象则用较低的质量显示,而其余内容(对象)则不显示。对于监控系统来说,在绝大部分时间内,监视画面的背景都保持不变,因此,在要求的比特率比较低时,对于监视画面的背景部分可以以较低的质量显示,这样并不会影响整个画面的效果。在MPEG-4发展的基础上,现又联合推出了更为优秀的H.264标准,目前新设计的系统,尤其是智能视频监控系统,大多采用此标准。 智能视频监控系统的产品形态之一是使用嵌入式视频服务器,这是一个基于客户机/服务器模型的系统,主要由现场采集设备、嵌入式视频服务器、传输网络以及监控终端组成。基于嵌入式视频服务器为核心的视频监控系统如图1所示。 嵌入式视频服务器硬件设计 工作流程为:服务器上电启动后,系统被加载到与嵌入式CPU相连的SDRAM中运行,CPU通过串口控制云台,转动摄像机获取视频信号,经过采样芯片实现A/D转换,转换后的数字视频数据传给MPEG-4或H.264音频/视频压缩芯片,完成MPEG-4或H.264视频压缩,压缩后的数据缓存于MPEG-4或H.264压缩芯片内的FIFO中,当FIFO半满时就触发主控CPU产生中断,由处理器的中断服务子程序获取该数据并存放于系统缓冲区中,等待发送程序读取。当服务器监听到监控端的视频请求时,服务器将视频数据打包并以流媒体的形式通过网络接口芯片传输到监控端上去。CPU同时接收监控端发来的控制信息,通过CGI(Common Gateway Interface)通用网关接口发送给应用程序。应用程序负责将控制信息通过RS232串口给摄像机云台。其功能层次关系如图3所示。 视频服务器主要元器件选择原则

音视频编解码芯片 ?芯片内集成有多个信号处理/控制单元,包括一个视频编码(压缩)器、一个视频解码(解压)器和一个片内CPU(内部扩展一个音频编码DSP、一个音频解码DSP、一个多路复合单元和一个多路解复合单元); ?具有可编程、高性能和低功耗特点,因为每个信号处理/控制单元都由一个RISC处理器和专用的硬件加速器构成。此外,视频编、解码器内部还集成了一个专用的SDRAM; ?在系统上电/复位时,视频编、解码器的固件程序可由外部主机(Host)载入各自专用的SDRAM;而编解码芯片内CPU的固件程序则可载入编解码芯片外挂的SDRAM; ?芯片的主机接口采用标准PCI接口,符合PCI总线规范2.2; ?为了使编、解码性能达到最佳,微处理器内部集成了一个多通道DMAC。系统Host可直接通过主机接口对编解码芯片进行控制,MPEG或H.264数据流采用DMA方式传输; ?提供兼容的I2C总线,可方便地对外围芯片进行控制。 I2C总线 |